- Modul D'Lorenzo

- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

- Jumper

Dalam rangkaian yang diberikan, terdapat penggabungan antara dua jenis flipflop, yaitu JK flipflop dan D flipflop. Rangkaian ini menggunakan switch SPDT sebagai input dan LED sebagai output. Switch SPDT terhubung ke sumber daya (power) dan ground, dimana kaki yang terhubung ke sumber daya menunjukkan logika 1, sedangkan yang terhubung ke ground menunjukkan logika 0. Untuk setiap variasi input yang diberikan, output dari kedua jenis flipflop diamati.

Baik J-K flipflop maupun D flipflop memiliki kaki input Set (S) dan Reset (R) yang keduanya beroperasi dengan prinsip active low. Artinya, jika salah satu kaki S atau R dalam kondisi aktif, output pada kaki Q dan Q' akan dipaksa menjadi nilai yang sesuai dengan kaki input yang aktif. Jika kaki S aktif, maka output kaki Q akan bernilai 1 dan kaki Q' akan bernilai 0. Sedangkan jika kaki R aktif, maka output kaki Q akan bernilai 0 dan kaki Q' akan bernilai 1. Jika kedua kaki S dan R aktif secara bersamaan, kedua input akan saling meniadakan efeknya, sehingga kedua flipflop akan melakukan operasi set dan reset secara bersamaan. Akibatnya, output dari kaki Q dan Q' akan bernilai 1 1.

Selanjutnya, jika kedua kaki S dan R tidak aktif atau diberikan input logika 1, kedua flipflop akan bekerja dengan prinsip input berikut:

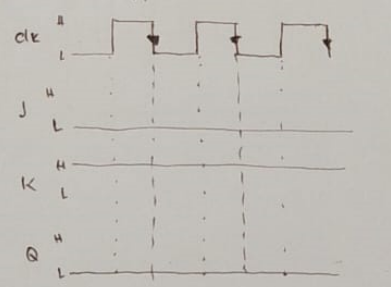

Pada J-K flipflop, terdapat tiga kaki input tambahan selain kaki S dan R, yaitu J, K, dan CLK. Kaki CLK (Clock) akan menentukan perubahan output berdasarkan input J-K yang diberikan. Dalam rangkaian ini, CLK beroperasi dengan prinsip active low, yang berarti setelah satu periode dan sinyalnya turun ke level rendah (low), output akan berubah sesuai dengan input J-K. Terdapat empat kondisi yang mungkin terjadi. Pertama, jika input J-K adalah 0-0, maka keadaan Q dan Q' tidak akan berubah dari keadaan sebelumnya. Kedua, jika input J-K adalah 1-0, maka keadaan Q dan Q' akan bernilai 1-0. Ketiga, jika input J-K adalah 0-1, maka keadaan Q dan Q' akan bernilai 0-1. Keempat, jika input J-K adalah 1-1, maka keadaan Q dan Q' akan berada dalam keadaan Toogle.

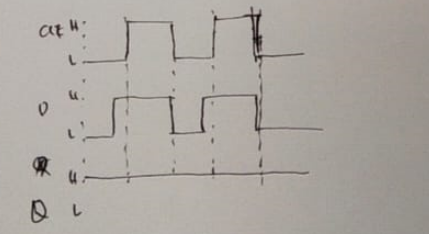

Pada D flipflop, terdapat dua kaki input tambahan selain kaki S dan R, yaitu D dan CLK. Kaki CLK juga menjadi penentu perubahan output berdasarkan input D yang diberikan. Dalam rangkaian ini, CLK beroperasi dengan prinsip active high, yang berarti setelah satu periode dan sinyalnya naik ke level tinggi (high), output akan berubah sesuai dengan input D. Terdapat dua kondisi yang mungkin terjadi. Pertama, jika input D adalah 0, maka keadaan Q dan Q' akan bernilai 0-1. Kedua, jika input D adalah 1, maka keadaan Q dan Q' akan bernilai 1-0.

Tidak ada komentar:

Posting Komentar